Recently, the Digilent open-source community has received several questions regarding how to implement the SPI interface on Zynq SoC and Zynq UltraScale+ MPSoC devices. After providing answers to these inquiries, I realized that it would be beneficial to write a detailed article explaining the process of implementing SPI communication on these platforms. This guide aims to help developers understand both the PS-side SPI controller and the PL-side AXI Quad SPI (QSPI) IP core options.

When working with Zynq SoC or Zynq UltraScale+ MPSoC in your design, there are two primary methods for implementing the SPI interface:

- Using the SPI controller available on the Processing System (PS) side, which includes two built-in SPI controllers.

- Implementing the AXI Quad SPI (QSPI) IP module on the Programmable Logic (PL) side, configured for standard SPI communication.

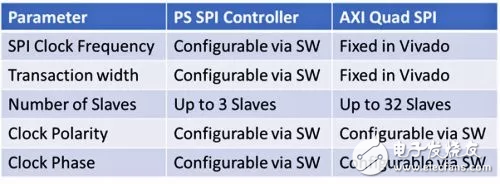

The choice between these two methods depends on your application requirements. Both implementations support all four SPI modes and can function as either master or slave. Below is a comparison of some key differences between the two approaches:

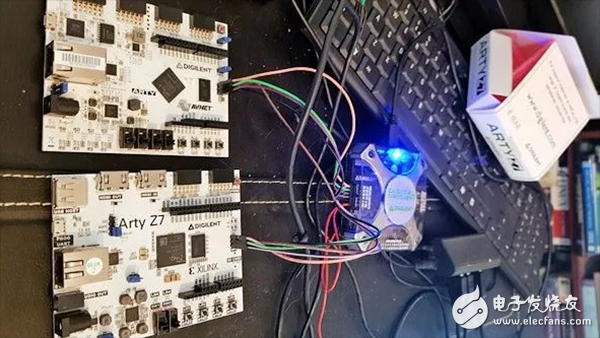

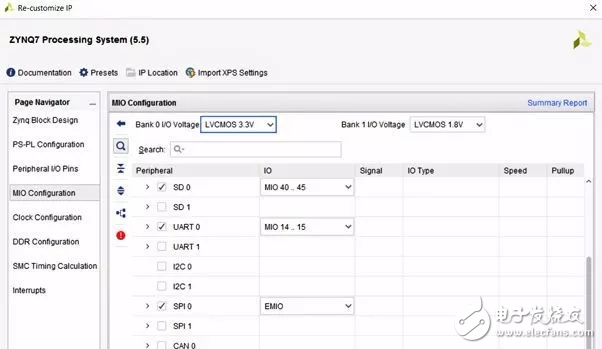

To begin with, we’ll demonstrate how to use the PS-side SPI controller for SPI communication. In the Zynq MIO Configuration tab, you can select the SPI interface and map the necessary pins to EMIO (External MIO) if required. For this example, I connected the SPI signals to the SPI interface of the Digilent Arty Z7 board, using EMIO to access the PL I/Os.

Figure: Enabling SPI and mapping ports to EMIO

Once the configuration is set, the next step is to connect the I/O pins correctly. The connections depend on whether you're configuring the SPI as a master or a slave. Each SPI port has input (xxx_i) and output (xxx_o) ports. Proper connection is crucial—incorrect wiring can lead to unexpected results and may take significant time to debug. Additionally, when acting as a slave, a Slave Select (SS) signal is required, while as a master, three select lines are typically used.

After setting up the I/O and generating the project, you can configure the SPI controller as a master or a slave using the SPI settings in your application. To interact with the PS-side SPI controller, you'll need to use the API functions provided by the BSP (Board Support Package), specifically those defined in `xspi_ps.h`. In our first example, we configured the SPI as a master.

By default, SPI transfers are 8-bit. However, you can also configure the system for 16-bit or 32-bit transfers. For 8-bit transfers, you can use the `u8` data type in C programs. For 16-bit or 32-bit transfers, you should use `u16` or `u32`, respectively. However, the API functions like `XSpiPs_Transfer` and `XSpiPs_PolledTransfer` expect buffers of type `u8`.

S32 XSpiPs_Transfer(XSpiPs *InstancePtr, u8 *SendBufPtr, u8 *RecvBufPtr, u32 ByteCount);

S32 XSpiPs_PolledTransfer(XSpiPs *InstancePtr, u8 *SendBufPtr, u8 *RecvBufPtr, u32 ByteCount);

To handle larger data types, you must cast the buffer to a `u8` pointer. For example:

XSpiPs_PolledTransfer(&SpiInstance, (u8*)&TxBuffer, (u8*)&RxBuffer, 8);

This setup allows you to send and receive 8-, 16-, or 32-bit data. To test this, I connected the SPI master to the Digilent Digital Discovery pocket instrument. I adjusted the software to send 16-bit data instead of 8-bit and verified the results using the oscilloscope.

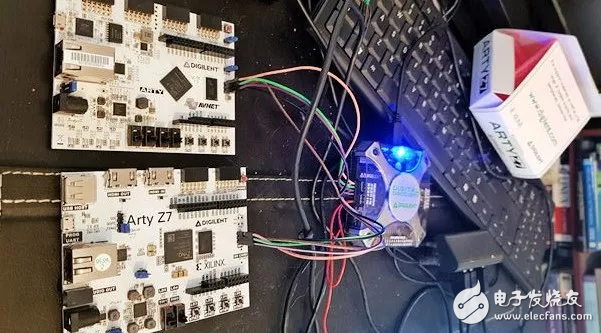

Figure: Arty Z7 development board with Digital Discovery pocket instrument

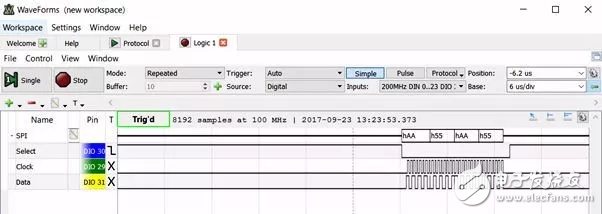

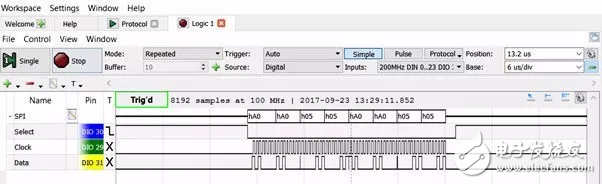

Figure: Zynq SoC PS SPI master sends four 8-bit words

Figure: PS SPI master sends four 16-bit words

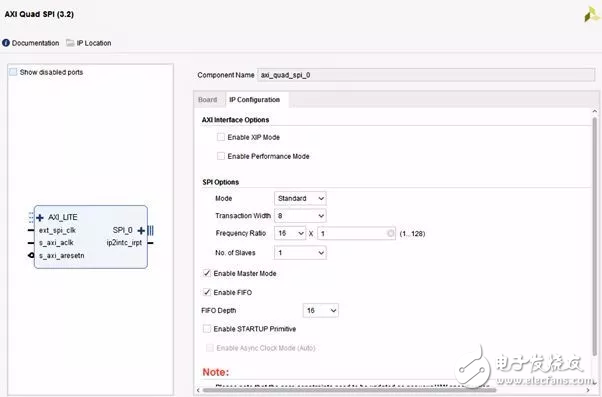

Another method involves using the AXI QSPI IP core. This approach requires more configuration in Vivado and takes longer to set up. In the AXI QSPI configuration window, you can adjust parameters such as bus width, clock frequency, and the number of slaves. The most critical setting is whether the QSPI core acts as a master or a slave. If you want it to operate as a master, enable the master mode option. If it's a slave, disable this option to ensure the presence of the SPISel input pin, which must be connected to the master’s slave select line.

Figure: Configuring the AXI Quad SPI

Photovoltaic Dual-Axis Tracking Bracket

Photovoltaic Dual-Axis Tracking Bracket,Completed Double axis System,Double axis System application,components of Dual Axis Solar Trackers

Hebei Shuobiao New Energy Technology Co., Ltd. , https://www.pvbracketsystem.com