Solar energy system, off gird pv system, grid pv system, solar power system, Solar Panel system, on grid solar system, grid tied solar system,20kw solar system

Solar energy system include Solar photovoltaic system: 1. Off grid photovoltaic system mainly consists of solar modules, controllers, and batteries. To supply power to AC loads, it is also necessary to configure an AC inverter. 2. Grid connected photovoltaic power generation system. 3. Distributed photovoltaic power generation system. Distributed power generation or distributed energy supply.

solar cell type

mono crystalline, half cut cell

solar energy pv system include

on grid system, off grid system, hybrid system

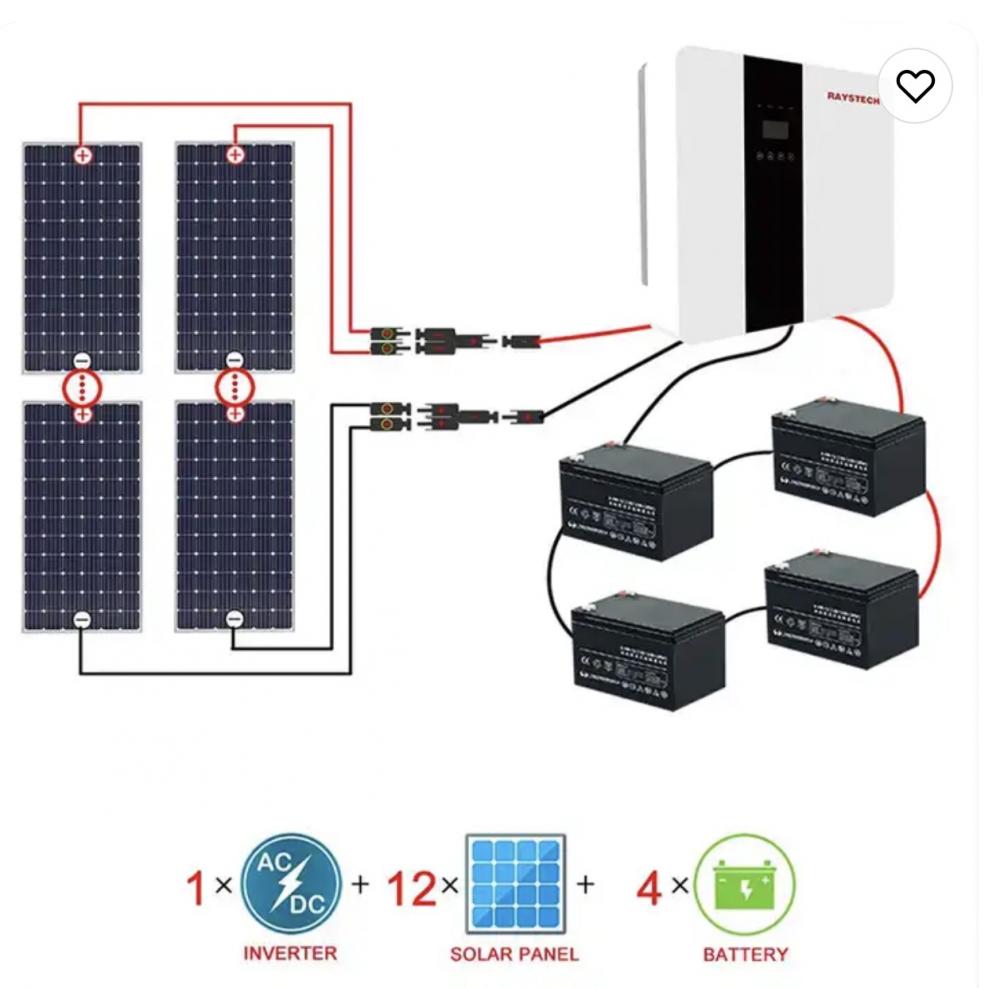

solar configuration

solar panel, inverter, battery, bracket cabels, mc4 connector

Product details and pic

Solar Engergy System,Gird Solar Power System,Pv System For Carport,Energy System Off Grid Solar System

PLIER(Suzhou) Photovoltaic Technology Co., Ltd. , https://www.pliersolar.com